- 您现在的位置:买卖IC网 > Sheet目录3872 > PIC18F4450T-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX16 44QFN

128

XMEGA A [MANUAL]

8077I–AVR–11/2012

Table 12-1. Interrupt levels.

The interrupt level of an interrupt request is compared against the current level and status of the interrupt controller. An

interrupt request of a higher level will interrupt any ongoing interrupt handler from a lower level interrupt. When returning

from the higher level interrupt handler, the execution of the lower level interrupt handler will continue.

12.6

Interrupt Priority

Within each interrupt level, all interrupts have a priority. When several interrupt requests are pending, the order in which

interrupts are acknowledged is decided both by the level and the priority of the interrupt request. Interrupts can be

organized in a static or dynamic (round-robin) priority scheme. High- and medium-level interrupts and the NMI will always

have static priority. For low-level interrupts, static or dynamic priority scheduling can be selected.

12.6.1 Static Priority

Interrupt vectors (IVEC) are located at fixed addresses. For static priority, the interrupt vector address decides the priority

within one interrupt level, where the lowest interrupt vector address has the highest priority. Refer to the device datasheet

for the interrupt vector table with the base address for all modules and peripherals with interrupt capability. Refer to the

interrupt vector summary of each module and peripheral in this manual for a list of interrupts and their corresponding

offset address within the different modules and peripherals.

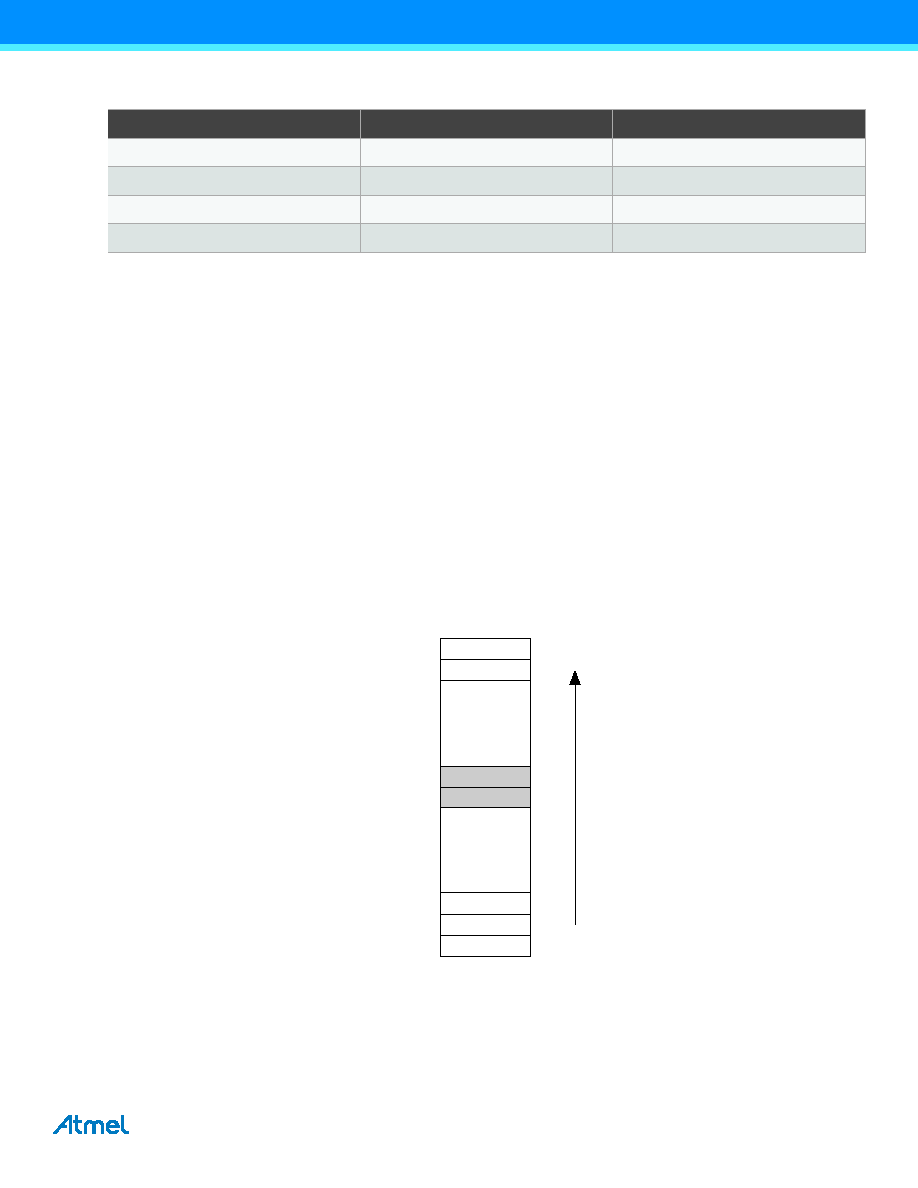

Figure 12-3. Static priority.

12.6.2 Round-robin Scheduling

To avoid the possible starvation problem for low-level interrupts with static priority, where some interrupts might never be

served, the PMIC offers round-robin scheduling for low-level interrupts. When round-robin scheduling is enabled, the

Interrupt Level Configuration

Group configuration

Description

00

OFF

Interrupt disabled.

01

LO

Low-level interrupt

10

MED

Medium-level interrupt

11

HI

High-level interrupt

IVEC 0

:

IVEC x

IVEC x+1

:

IVEC N

Lowes t Priority

Highes t Priority

Lowes t Addres s

Highes t Addres s

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F4321T-I/ML

IC PIC MCU FLASH 4KX16 44QFN

PIC18F4221T-I/ML

IC PIC MCU FLASH 2KX16 44QFN

PIC18F2321T-I/ML

IC PIC MCU FLASH 4KX16 28QFN

PIC18F2221T-I/SO

IC PIC MCU FLASH 2KX16 28SOIC

PIC16LF1939-I/MV

IC MCU 8BIT 28KB FLASH 40-UQFN

PIC24F16KL402-I/SP

IC MCU 16BIT 16KB FLASH 28-SPDIP

PIC18F24J11-I/SS

IC PIC MCU FLASH 16K 2V 28-SSOP

PIC24F16KA101-I/SO

IC PIC MCU FLASH 16K 20-SOIC

相关代理商/技术参数

PIC18F4450T-I/PT

功能描述:8位微控制器 -MCU 16KB FL 768 RAM 34 I/O FS-USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-BL

制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB; Silicon Manufacturer:Powerlite Systems; Core Architecture:PIC; Kit Contents:Board; Features:Bootloader Programming, RS232 Connector for Boot-Loading and Serial Comms ;RoHS Compliant: Yes

PIC18F4455-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/P

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4458-I/ML

功能描述:8位微控制器 -MCU 24KB Flash 2KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT